74ls86逻辑图

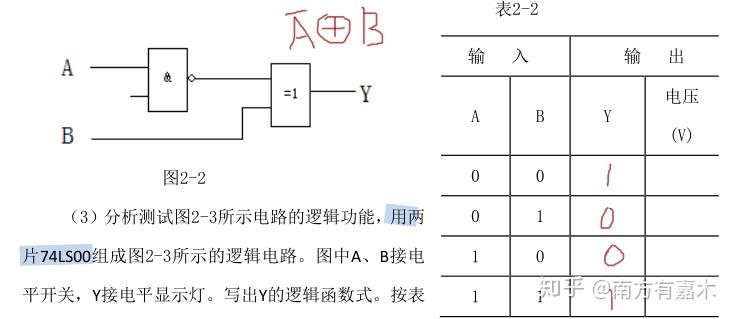

(4)依次测试与非门(74ls00),或非门(74ls02),异或门(74ls86)的测逻辑

图片尺寸499x277

异或门74ls86

图片尺寸1080x810

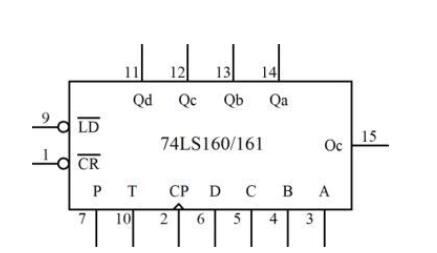

74ls160数字逻辑芯片的工作原理

图片尺寸437x253

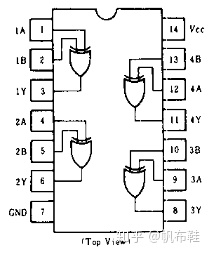

74ls86 四2输入异或门

图片尺寸713x537

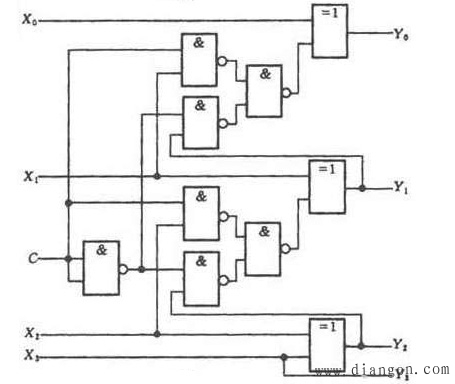

一位全加器电路实现如下: 图中,用74ls00d代替74hc86n 如果要实现多为

图片尺寸893x417

74ls86引脚管脚功能资料74l|2017-04-1374ls86引脚图与管脚功能表资料

图片尺寸614x438

与门74ls32或门74ls86 异或门not(proteus中的非门)·逻辑表达式:a

图片尺寸735x319

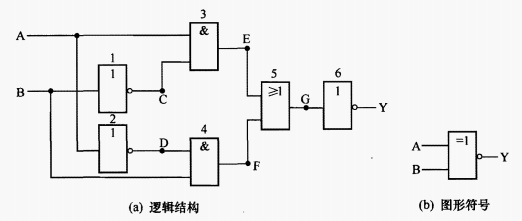

b a y2 b c b 2, 测试用异或门(74ls86)和与非门组成的半加器的逻

图片尺寸278x334

15二进制并行加减法电路二进制并行加减法sn74ls86sn74ls283|2012-11

图片尺寸963x491

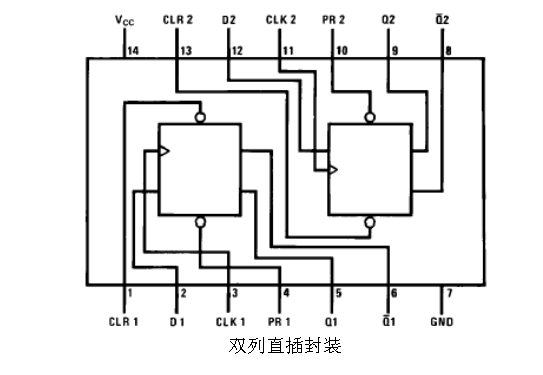

clr:复位信号(低电平有效)pr:置位信号(低电平有效)q=d74hc86:74hc

图片尺寸543x375

实验原理 (3)器件功能: 74ls86 器件功能: 异或门的逻辑功能:不同 ""

图片尺寸1080x810

测试用异或门(74ls86)和与非门组成的半加器的逻辑功能.

图片尺寸395x272

实验12: 组合逻辑电路-一位全加器

图片尺寸501x415

采用小规模集成器件的组合逻辑电路设计

图片尺寸455x384

实验3 组合逻辑电路设计

图片尺寸478x313

由( 3) 式和( 5)式可知要用2 个异或门( 1 个74l s86) 和3 个与非

图片尺寸353x226

同或门74ls86是一个4组2输入异或门芯片,内部有4组异或门,每组异或门

图片尺寸522x221

有没有一种芯片或电路可以实现高低电平交替输出?

图片尺寸600x278

74ls86 此为或非门芯片为74ls00从上至下

图片尺寸554x328

使用到的芯片异或门芯片(74ls86),与门芯片(74ls08),为了

图片尺寸211x257